제품소개

Avery Design

Avery Design Systems is an established EDA business supplying semiconductor industry with spectrum of focused solutions

- · SystemVerilog/UVM Verification IP portfolio

- · Virtual host/embedded QEMU and VIP/RTL system co-simulation

- · Semi-Formal applications for X-verification

- · Simulation acceleration (FPGA-based), FPGA tools, and Prototyping IPs

Product Lines – RTL Design & Verification

Verification IP

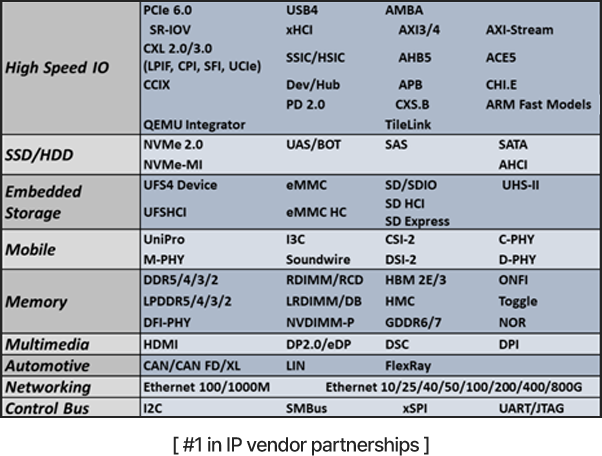

· 60+ standard protocols

· Most complete VIP solution

- ·Robust and flexible BFMs

- ·Protocol checking

- ·SoC/IP compliance testsuites

- ·Protocol analyzer trace logs

- ·Functional coverage

- ·Intelligent Scoreboard

- ·Native SystemVerilog/UVM

· Flexible licensing

- ·Protocol-specific

- ·VIP Portfolio

· Compliance verification services

·Leader in SSD/HDD VIPs

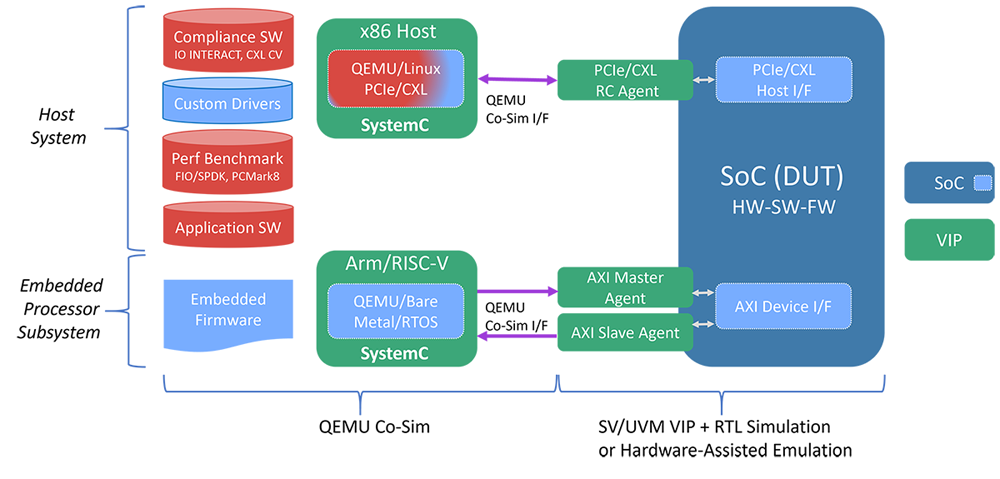

System-Level QEMU Co-Simulation

· Level up and perform full System HW-SW verification at pre-silicon level

- ·Iterate HW and SW changes 10X faster at RTL compared to FPGA or system prototypes

- ·Begin HW-SW integration much sooner in development process

· Virtual machine to VIP co-sim/co-emulate environment extends existing SV/UVM testbench + VIPs

· Run OS and SW unmodified from actual system configuration

· Debug trace shows QEMU to remote PCIe/CXL/AXI ports transactions

· Avery's implementation of QEMU co-simulation is optimized for fastest performance including KVM mode and iWARP technology

· Simulations are scalable to 10s to 100s of instances for regression over OS versions and HW configurations

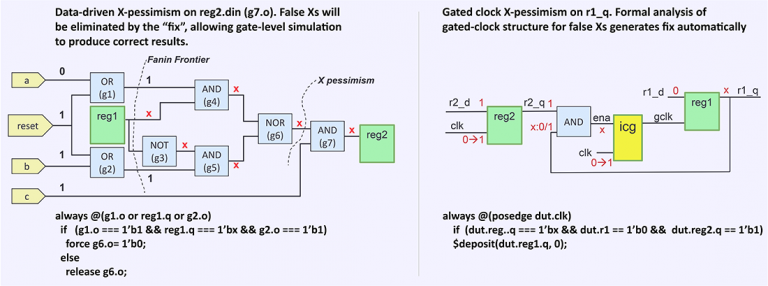

SimXACT – Gate Simulation Productivity and Analysis Technology

· Solution to automatically eliminate X-pessimism in GLS

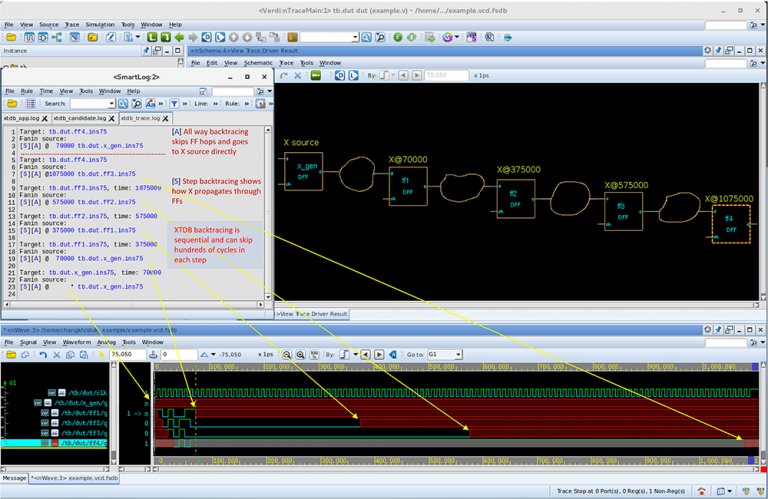

· Sequential X backtrace analysis

· Add-on to VCS/Xcelium/Questa*

SimCluster GLS

· Parallel distributed simulation for gate-level (Zero, Unit, Full SDF)

· Add-on to VCS/Xcelium/Questa

· 3-5X GLS simulation speedup

· Optional SimXACT mode

SimAccel FPGA-based Simulation Accelerator

· > 100-1000X speedup over simulation only

· Accelerator System IP

· Accelerated VIP

· Virtual host/embedded QEMU/Arm Fast Models co-emulation and embedded co-debug extensions to GDB

· Multi-FPGA partitioner

· Runs on commodity FPGA prototyping systems